近年来,无缺陷的中性原子阵列因其高扩展性和高可编程性的特点,成为了受到广泛关注的量子模拟和计算平台。为了获得无缺陷的阵列,需要对初始随机装载的原子进行重新排列,以达到目标构型。重排的总时间成本包括原子检测、原子占据分析、重排策略制定、驱动波形生成和原子移动等步骤。然而,随着阵列规模的增大,重排的时间成本会增加,而被光镊囚禁的原子也更容易逃逸。这成为了阻碍更大规模阵列实现的基本限制之一。

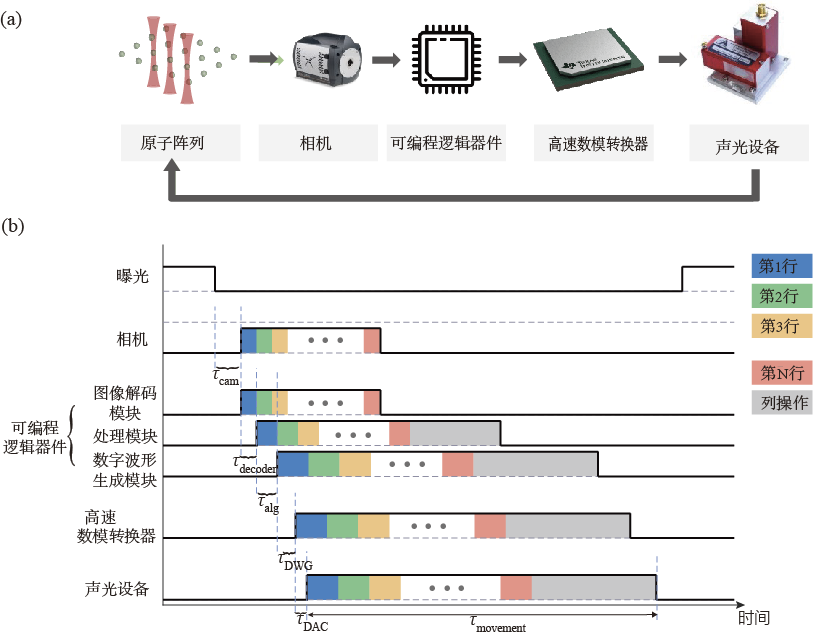

目前绝大多的重排系统采用电脑、图像采集卡和任意波形发生器的结构,需要通过电脑接收相机发来的数据、分析原子位置分布、通过算法决定如何将初始的随机分布的原子分配到目标位置、再生成相应的射频信号来驱动原子的移动。为了进一步降低时间消耗,陈文兰课题组设计了一种基于现场可编程门阵列(FPGA)的新型控制系统,在单芯片上实现图像采集、占据数分析、算法决策、任意波形生成和原子移动控制(图1(a))。

图1:(a)重排控制流。(b)系统的典型时序。

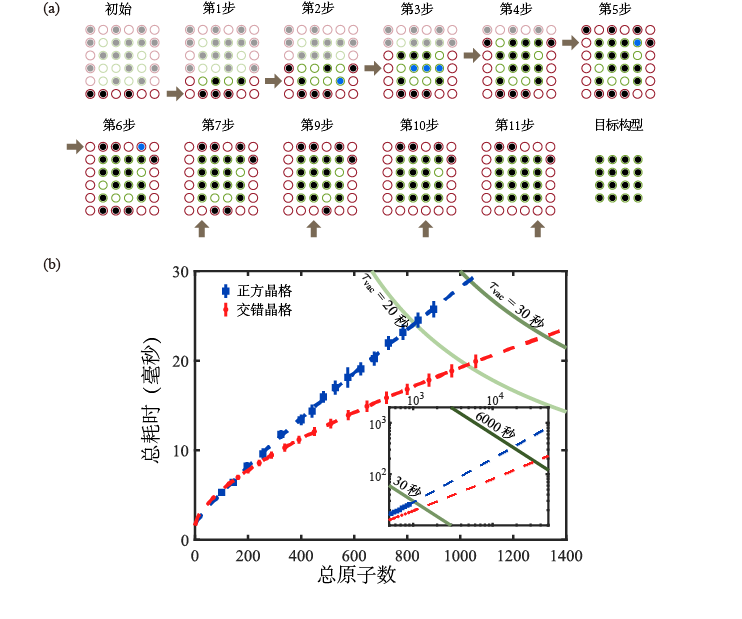

同时,他们还提出了一种新的名为“俄罗斯方块算法”的重排算法,可以实现二维任意几何结构的并行重排。对L×L的目标构型,总的移动步数最高为2L(图2),相比于之前的算法有标度上的优势;且无需等待相机读出整张图片就可以开始重排。

图2:俄罗斯方块算法的图解。(a)算法举例:从6×6的初始装载到4×4的目标构型。(b):不同目标原子数下的时间消耗。

这些特性使得所有的模块可以流水线式地工作,在重新排列过程中节省大量时间。通过测试,发现可以快速重新排列原子阵列(图2(b)),使得实现室温下1000个原子、低温环境下10000个原子的无缺陷阵列成为可能。该重排系统是对目前中性原子量子计算平台的重要改进,并可立即应用于当前的量子计算机中,并为量子反馈、线路中操作等量子操控技术提供了新的解决方案。

该研究成果以“Accelerating the Assembly of Defect-Free Atomic Arrays with Maximum Parallelisms”为题发表于 Physical Review Applied(Phys. Rev. Applied 19, 054032)。清华大学物理系的陈文兰教授为该工作的通讯作者,清华大学物理系2019级博士生王帅,2022级博士生张文军和2020级博士生张韬为该工作的共同第一作者。参与者包括清华大学胡嘉仲教授、本科生梅树尧、博士生王雨晴。该成果获得了国家重点研发计划、国家自然科学基金等部门的经费支持和帮助。

文章链接:

https://link.aps.org/doi/10.1103/PhysRevApplied.19.054032